The SERENA project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 779305.

SEREN

# SERENA webinar series Heterogeneous Integration for High Performance mmWave Electronics

Franz Dielacher

Infineon Technologies Austria AG

Franz.Dielacher@infineon.com

2021, remote

gan-on-Silicon Efficient mm-wave euRopean systEm iNtegration plAtform

# OUTLINE

SFRFN

- Functional split on system level

- RF Technology considerations for Core-chip (RF-beamformer) implementation

- Core-chip design

- Features

- Functional block diagram

- Measured performance

- Summary

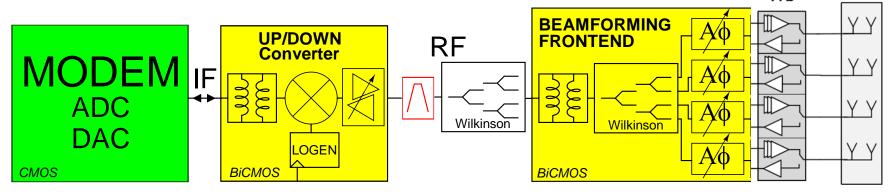

# System overview / functional split

- Up-down conversion and beamforming split into separate ICs

- Flexibility

- RFICs cover all frequency bands

- External filter adapted to the chosen band

- Quad-channel beamforming RFIC

- Shortest connections to antennas

- Effective cooling

Copyright  $\ensuremath{\mathbb{C}}$  Infineon Technologies AG 2021. All rights reserved.

### SEREN

# OUTLINE

- Functional split on system level

- RF Technology considerations for Core-chip (RF-beamformer) implementation

- Core-chip design

- Features

- Functional block diagram

- Measured performance

- Summary

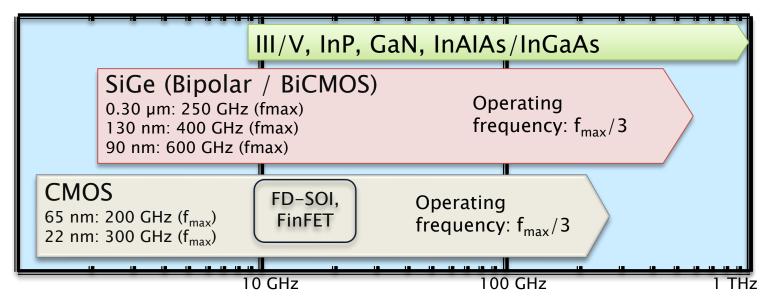

### **IC Technology Choice – focus on RF**

SiGe-HBT: 4x better gm/IDS, Higher voltage (output power), .....

FD-SOI: Dynamical modulation of threshold voltage of devices, .....

GaN HEMT: record power below 100GHz, .....

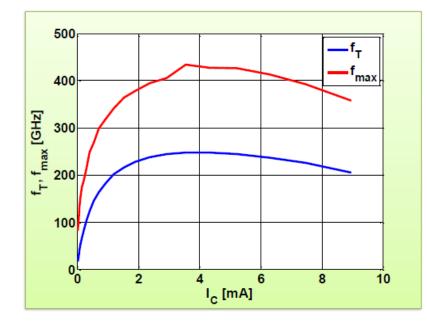

### **130nm SiGe-BiCMOS technology features**

| BV <sub>ceo</sub> | BV <sub>cbo</sub> | $BV_{ebo}$ |

|-------------------|-------------------|------------|

| 1,5V              | 5,3V              | 2V         |

130nm SiGe-BiCMOS:  $f_{max} = 400 \text{ GHz}$ f<sub>T</sub> = 250 GHz  $J_{\rm C} \sim 13 \text{ mA/}\mu\text{m}^2$ Min. Gate Delay ~ 2.3 ps Substrate: p, 20  $\Omega$ cm, 8" Base Layer: SiGe:C TaN Resistor and MIM-Cap Metallization: 6 L Copper + 1 L Top Al (two thick top Cu layers)

SEREN

# OUTLINE

SFRFN

- Functional split on system level

- RF Technology considerations for Core-chip (RF-beamformer) implementation

- Core-chip design

- Features

- Functional block diagram

- Measured performance

- Summary

### SEREN

## **Core Chip Objectives**

- Highly integrated SiGe-BiCMOS beamforming RFIC:

- Quadruple channels

- Rx/Tx TDD operation

- 5 Bidirectional RF ports

- Integrated LNA and PA

- > 30dB of programmable gain control

- Full 360° digitally controlled phase shifter (96 states)

- ◆ Fast ( < 1µs) digital control using look-up table</li>

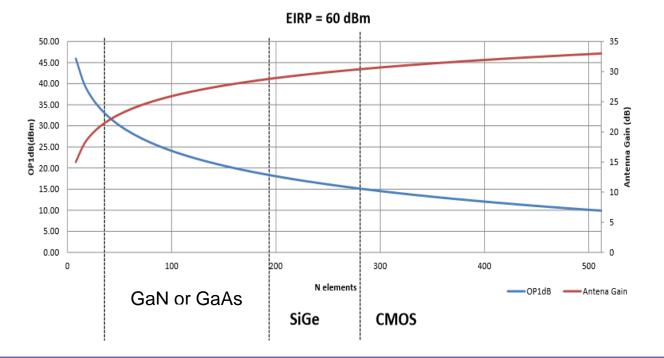

Power Amplifier Technology Selection vs. Array Size

Backoff in the calculation below is 10dB

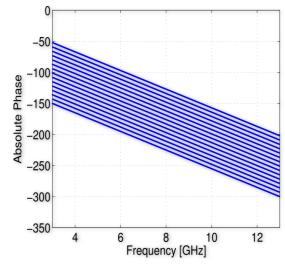

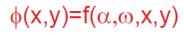

### **Phase Shifter versus True Time Delay**

Wideband Phase Shifter

(wide carrier frequency range)

Group Delay

$\tau(\mathbf{x},\mathbf{y})=\mathbf{f}(\alpha,\mathbf{x},\mathbf{y})$

Variable TTD (instead of variable phase shifter) supports wideband signals.

SEREN/

Low-loss, linear, compact RF variable delays are hard to implement.

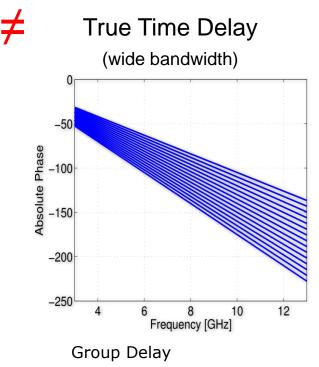

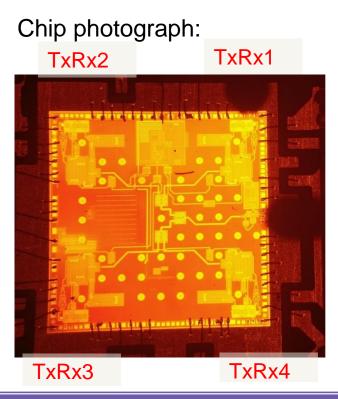

### **Quadchannel RX/TX 39GHz Beamforming RFIC**

37GHz to 43GHz frequency range

SEREN

- Over 30dB of amplitude control

- Phase/ delay control based on digitally programmable delay lines providing 360° of phase control range or at least 15ps of true time delay control

- RF Built-In Test Equipment

including PLL and ADC

SEREN

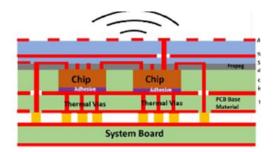

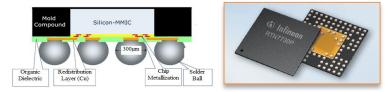

# **Packaging options**

### SERENA: Packaging by 'Chip-Embedding' and AiP

#### eWLB (embedded Wafer Level Ballgrid-Array) Packaging

### **RFIC small signal performance**

### TRANSMIT

Max gain and max delay configuration

- Gain>32dB over 37GHz - 43GHz

- Peak gain of 38dB

- Input matching better -15dB over 37GHz – 43GHz

- Output matching better -10dB over 37GHz – 43GHz

### RECEIVE

Max gain and max delay configuration

SEREN

- Peak gain of 10dB

- Input/output matching better -12dB over 37GHz – 43GHz

- NF of <6dB at ambient temperature</li>

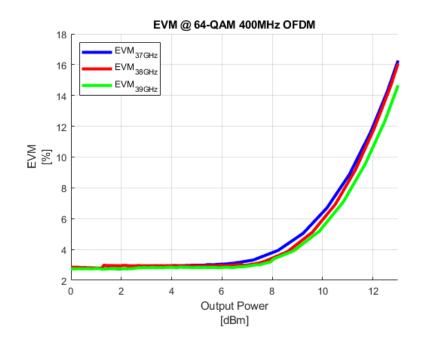

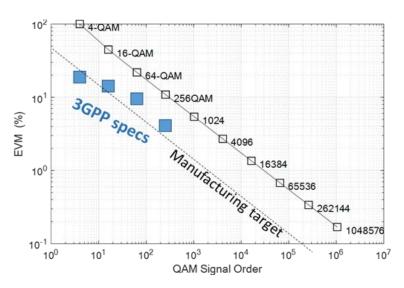

# **EVM measurements**

EVM Required to Support Different Orders of Modulation, as Extrapolated from 3GPP Metrics Courtesy of Earl McCune

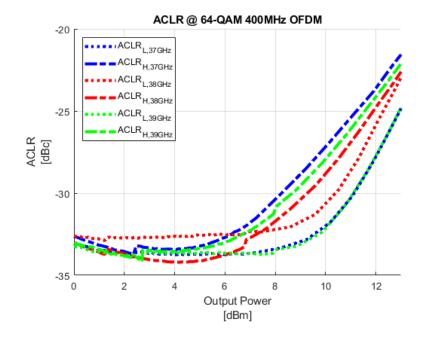

# **ACLR measurements**

Establishing translations between circuit and radiated performance is challenging

Beamforming and AAS/massive MIMO implies new challenges due to e.g. antenna cross talk etc.

# OUTLINE

SFRFN

- Functional split on system level

- RF Technology considerations for Core-chip (RF-beamformer) implementation

- Core-chip design

- Features

- Functional block diagram

- Measured performance

- Summary

### Summary

- SiGe-BiCMOS is a performance and cost efficient technology for this application

- Low-loss, linear and digitally programmable delay lines successfully implemented

- Integrated BITE is very useful for circuit-test and calibration

- PA becomes the bottleneck and has to be addressed at all levels including technology selection and architecture Significant improvement needed for volume deployment (like fineline GaN technology, Doherty PA with RF predistortion, Relaxed ACLR specification, ...)

### Acknowledgements

Special thanks to:

D. Dal Maistro, C. Rubino, M. Caruso, M. Tiebout, I. Maksymova, M. Ilic, P. Thurner, M. Zaghi, K. Mertens, E. Schatzmayr, M. Druml, R. Druml, M. Mueller, M. Anderwald, J. Wuertele, U. Rueddenklau, Yannis Papananos and Simone Erba

# SERENA Grant Agreement No. 779305

"The SERENA project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 779305."

If you need further information, please contact the coordinator: TECHNIKON Forschungs- und Planungsgesellschaft mbH Burgplatz 3a, 9500 Villach, AUSTRIA Tel: +43 4242 233 55 Fax: +43 4242 233 55 77 E-Mail: coordination@serena-h2020.eu

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author`s view – the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.